|

жұҪиҪҰз”өеӯҗ |

|

| жҢүиЎҢдёҡзӯӣйҖү |

|

|

| жҢүдә§е“ҒзӯӣйҖү |

|

|

| |

|

жҹҘзңӢжң¬зұ»е…ЁйғЁж–Үз« |

| |

|

|

|

|

Speedcore eFPGAеңЁжұҪиҪҰжҷәиғҪеҢ–дёӯзҡ„еә”з”Ё |

|

|

дҪңиҖ…пјҡAchronixеҚҠеҜјдҪ“е…¬еҸё |

|

жҰӮиҝ°

ж— и®әдёҖиҫҶжұҪиҪҰе®ғжҳҜ21дё–зәӘ20е№ҙд»ЈеҲқзҡ„иҫ…еҠ©й©ҫ驶жұҪиҪҰпјҢеҚіеёҰжңүз”ЁдәҺдҝЎжҒҜеЁұд№җзі»з»ҹгҖҒдј еҠЁзі»з»ҹе’ҢиҮӘдё»й©ҫ驶е‘ҳиҫ…еҠ©зі»з»ҹпјҲADASпјүзҡ„жҷәиғҪеӯҗзҪ‘зҡ„жұҪиҪҰпјҢиҝҳжҳҜжңӘжқҘ3зә§ пјҲLevel 3пјүеҸҠд»ҘдёҠзҡ„иҮӘеҠЁй©ҫ驶жұҪиҪҰпјҲеңЁиҪҰжөҒдёӯй©ҫ驶时еҸӘйңҖжңҖе°‘зҡ„дәәеҠӣиҫ…еҠ©пјүпјҢзҪ‘з»ңеҢ–дәӨйҖҡзі»з»ҹеҜ№зЎ¬д»¶еҠ йҖҹзҡ„йңҖжұӮжӯЈеңЁиҝ…зҢӣеўһй•ҝгҖӮеҮ е№ҙеүҚпјҢз”ұNvidiaпјҢMobileyeе’Ңе…¶д»–д»ҘCPUдёәдёӯеҝғзҡ„дҫӣеә”е•ҶжҺЁеҮәзҡ„жңҖеҸ—йқ’зқҗзҡ„жұҪиҪҰжҷәиғҪжЁЎеһӢйғҪеҒҮи®ҫдәҶдёҖдёӘйӣҶдёӯејҸжұҪиҪҰзҪ‘з»ңпјҢе…¶дёӯз”ұеёҰжңүеўһејәDSPеҠҹиғҪзҡ„еӨҡж ёRISC CPUжқҘз®ЎзҗҶдёҖеҘ—дё“з”Ёзҡ„еӯҗзҪ‘з»ңгҖӮзҺ°еңЁпјҢе…іжіЁзӮ№жӯЈеңЁиҝ…йҖҹиҪ¬еҗ‘еҲҶеёғејҸжұҪиҪҰжҷәиғҪеҢ–пјҢе…¶дёӯеҢ…еҗ«еёҰжңүзӣёе…іи§Ҷи§үзі»з»ҹзҡ„еӨҚжқӮзӣёжңәпјҢе…·жңүжқҘиҮӘзү©иҒ”зҪ‘дё–з•Ңзҡ„дј ж„ҹеҷЁдёӯжһўжһ¶жһ„зҡ„дј ж„ҹеҷЁеӯҗзҪ‘з»ңгҖҒд»ҘеҸҠз”ЁдәҺиҪҰиҪҪдҝЎжҒҜеЁұд№җзі»з»ҹпјҲIVIпјүе’ҢADASзҡ„йҷ„еҠ еӯҗзҪ‘з»ңгҖҒд»ҘеҸҠдј еҠЁзі»з»ҹ/еҠЁеҠӣзі»з»ҹеӯҗзҪ‘з»ңпјҢе…ұеҗҢеҚҸдҪңжқҘе®һзҺ°иҮӘеҠЁй©ҫ驶жұҪиҪҰеҠҹиғҪгҖӮ

иҷҪ然Achronixйў„и®ЎжңӘжқҘзҡ„дј з»ҹиҪҰиҫҶе’ҢиҮӘеҠЁй©ҫ驶иҪҰиҫҶжңҖе–ңж¬ўзҡ„жһ¶жһ„йғҪе°ҶжҳҜеҲҶеёғејҸжһ¶жһ„пјҢдҪҶжҳҜд»»дҪ•дёҖз§ҚзҪ‘з»ңйғҪйңҖиҰҒжҜ”зӣ®еүҚе·Із»Ҹе®һзҺ°зҡ„жһ¶жһ„жӣҙеӨҡзҡ„еҗҺеӨҮеҚҸеӨ„зҗҶиғҪеҠӣгҖӮжұҪиҪҰзҪ‘з»ңдёӯйў„жңҹзҡ„еҲҶеёғејҸи®Ўз®—жһ¶жһ„е°ҶжҳҜејӮжһ„зҡ„пјҢйңҖиҰҒд»ҺзҪ‘з»ңжҺ§еҲ¶еҲ°еҲ©з”Ёж·ұеәҰеӯҰд№ иҠӮзӮ№зҡ„并иЎҢеҜ№иұЎиҜҶеҲ«зҡ„ж··еҗҲи®Ўз®—иө„жәҗгҖӮз»“жһңпјҢиұӘеҚҺиҫ…еҠ©й©ҫ驶жұҪиҪҰдёӯзӣ®еүҚCPUзҡ„еҹәж•°еӨҡиҫҫ100дёӘпјҢиҖҢеңЁиҮӘеҠЁй©ҫ驶жұҪиҪҰдёӯеҸҜиғҪдјҡеўһеҠ еҲ°еҮ зҷҫдёӘCPUгҖӮдј ж„ҹеҷЁдёӯжһўе°ҶйңҖиҰҒеҗҺеӨҮеӣҫеғҸеӨ„зҗҶжқҘе®һзҺ°жүӯжӣІе’ҢжӢјжҺҘж•Ҳжһңпјӣд»ҘеӨӘзҪ‘йңҖиҰҒIPиҝӣиЎҢж•°жҚ®еҢ…иҝҮж»Ө/зӣ‘жҺ§пјҢд»ҘеҸҠдёҺдј з»ҹCANе’ҢFlexRayзҪ‘з»ңзҡ„зү№ж®ҠжЎҘжҺҘгҖӮеңЁз¬¬дёҖд»ЈжұҪиҪҰжһ¶жһ„дёӯдҪҝз”Ёж•ҙж•°дёӘCPUе’ҢGPUпјҢе°ҶиҝҒ移еҲ°йңҖиҰҒеҸҜзј–зЁӢеҠ йҖҹзҡ„й«ҳеәҰдё“дёҡеҢ–и®Ўз®—иҠӮзӮ№гҖӮ

дёәдәҶдјҳеҢ–иҠҜзүҮйқўз§Ҝе’ҢеҠҹзҺҮж•ҲзҺҮпјҢеңЁжңӘжқҘзҡ„жұҪиҪҰе№іеҸ°дёҠпјҢзӣёжҜ”еӣәе®ҡеҠҹиғҪзҡ„SoCжҲ–дј з»ҹзҡ„FPGAпјҢе°ҶSpeedcoreв„ўеөҢе…ҘејҸFPGAпјҲeFPGAпјүзЎ…зҹҘиҜҶдә§жқғпјҲIPпјүйӣҶжҲҗеҲ°SoCдёӯд»ҘжҸҗдҫӣе®ўжҲ·еҸҜй…ҚзҪ®еҠҹиғҪпјҢжҳҜе®һзҺ°еҝ«йҖҹеҲҮжҚўеҚҸеӨ„зҗҶзҡ„дёҖдёӘжңҖдҪійҖүжӢ© гҖӮиҰҒдәҶи§ЈжӣҙеӨҡе…ідәҺеӨ„зҗҶиҝҮзЁӢзҡ„жј”еҸҳпјҢиҜ·еҸӮи§ҒAchronixзҷҪзҡ®д№ҰпјҲWP008пјүпјҡSoCдёӯзҡ„EFPGAеҠ йҖҹ - дәҶи§ЈSpeedcore IPи®ҫи®ЎжөҒзЁӢгҖӮ

Speedcore eFPGA IPеңЁејӮжһ„жұҪиҪҰж•°жҚ®еӨ„зҗҶдёӯзҡ„зӢ¬зү№дҪңз”Ё

Speedcore eFPGA IPеҸҜд»ҘйӣҶжҲҗеҲ°ASICжҲ–SoCдёӯпјҢд»ҘжҸҗдҫӣе®ҡеҲ¶зҡ„еҸҜзј–зЁӢйҖ»иҫ‘йҳөеҲ—гҖӮе®ўжҲ·жҢҮе®ҡ他们зҡ„йҖ»иҫ‘гҖҒеҶ…еӯҳе’ҢDSPиө„жәҗйңҖжұӮпјҢ然еҗҺAchronixй…ҚзҪ®Speedcore IPд»Ҙ满足他们зҡ„зү№е®ҡйңҖжұӮгҖӮSpeedcoreжҹҘжүҫиЎЁпјҲLUTпјүгҖҒRAMжЁЎеқ—е’ҢDSP64жЁЎеқ—еҸҜд»ҘеғҸз§ҜжңЁдёҖж ·иҝӣиЎҢз»„еҗҲпјҢдёәд»»дҪ•з»ҷе®ҡеә”з”ЁеҲӣе»әжңҖдҪізҡ„еҸҜзј–зЁӢйҖ»иҫ‘йҳөеҲ—гҖӮSpeedcore eFPGA IPеңЁжұҪиҪҰзҪ‘з»ңйӣҶжҲҗж–№йқўжҸҗдҫӣзӢ¬зү№зҡ„дјҳеҠҝпјҢж— и®әжҳҜеңЁзҺ°жңүи®ҫи®ЎдёӯеҸ–д»ЈдёҖдёӘFPGAиҝҳжҳҜеўһејәдёҖдёӘASICгҖӮ

пҒ¬жӣҙй«ҳзҡ„жҖ§иғҪ вҖ“ дёҖдёӘeFPGAйҖҡиҝҮе®Ҫйҳ”зҡ„并иЎҢжҺҘеҸЈзӣҙжҺҘиҝһжҺҘпјҲж— I / Oзј“еҶІеҷЁпјүеҲ°ASICпјҢжҸҗдҫӣжҳҫи‘—жӣҙй«ҳзҡ„еҗһеҗҗйҮҸпјҢ延иҝҹд»…дёәдёӘдҪҚж•°зҡ„ж—¶й’ҹе‘ЁжңҹгҖӮ еңЁйңҖиҰҒеҜ№иҝ…йҖҹеҸҳеҢ–зҡ„дәӨйҖҡзҠ¶еҶөиҝӣиЎҢе®һж—¶е“Қеә”ж—¶пјҢ延иҝҹйқһеёёйҮҚиҰҒгҖӮ

пҒ¬жӣҙдҪҺзҡ„еҠҹиҖ—пјҡ

пҒ¬еҸҜзј–зЁӢI / Oз”өи·Ҝзҡ„еҠҹиҖ—еҚ зӢ¬з«ӢFPGAжҖ»еҠҹиҖ—зҡ„дёҖеҚҠгҖӮдёҖдёӘ eFPGAзӣҙжҺҘиҝһжҺҘеҲ°SoCпјҢе®Ңе…Ёж¶ҲйҷӨдәҶеӨ§еһӢеҸҜзј–зЁӢI / Oзј“еҶІеҷЁпјҢд»ҺиҖҢйҷҚдҪҺдәҶеҠҹиҖ—гҖӮ

пҒ¬дёҖдёӘeFPGAзҡ„йқўз§ҜеҸҜд»Ҙж №жҚ®жңҖз»Ҳеә”з”Ёзҡ„иҰҒжұӮзІҫзЎ®е®ҡеҲ¶пјҢ并且еҸҜд»Ҙи°ғж•ҙе·ҘиүәжҠҖжңҜд»Ҙе®һзҺ°жҖ§иғҪе’ҢеҠҹиҖ—зҡ„е№іиЎЎгҖӮ

пҒ¬жӣҙдҪҺзҡ„зі»з»ҹжҲҗжң¬пјҡ

пҒ¬дёҖдёӘeFPGAзҡ„зүҮиҠҜеҚ з”Ёйқўз§ҜжҜ”зӯүж•Ҳзҡ„зӢ¬з«ӢFPGAе°Ҹеҫ—еӨҡпјҢиҝҷжҳҜеӣ дёәеҸҜзј–зЁӢI / Oзј“еҶІеҷЁпјҢжңӘдҪҝз”Ёзҡ„DSPе’ҢеӯҳеӮЁеҷЁжЁЎеқ—д»ҘеҸҠиҝҮеәҰй…ҚзҪ®зҡ„LUTе’ҢеҜ„еӯҳеҷЁйғҪе…ЁйғЁиў«з§»йҷӨгҖӮ

пҒ¬еҖҹеҠ©Speedcoreе®ҡеҲ¶жЁЎеқ—пјҢеҸҜе°Ҷе®ҡеҲ¶еҠҹиғҪдҪңдёәйҷ„еҠ жЁЎеқ—ж·»еҠ еҲ°eFPGAйҖ»иҫ‘йҳөеҲ—дёӯпјҢ并дёҺдј з»ҹзҡ„LUTгҖҒRAMе’ҢDSPжһ„е»әжЁЎеқ—дёҖиө·ж·»еҠ гҖӮиҝҷз§Қй«ҳж•Ҳзҡ„е®һж–Ҫж–№ејҸжһҒеӨ§ең°йҷҚдҪҺдәҶзүҮиҠҜе°әеҜёйқўз§ҜпјҢжңҖеӨ§йҷҗеәҰең°йҷҚдҪҺдәҶеҠҹиҖ—пјҢе…¶жҖ»дҪ“з»“жһңе°ұжҳҜпјҢеӨ§еӨ§йҷҚдҪҺдәҶзі»з»ҹжҲҗжң¬гҖӮжңүе…іжӣҙеӨҡиҜҰз»ҶдҝЎжҒҜпјҢиҜ·еҸӮйҳ…AchronixзҷҪзҡ®д№ҰпјҲWP009пјүпјҡдҪҝз”ЁSpeedcoreе®ҡеҲ¶жЁЎеқ—жқҘеўһејәeFPGAеҠҹиғҪгҖӮ

пҒ¬жӣҙй«ҳзҡ„зі»з»ҹеҸҜйқ жҖ§е’ҢиүҜзҺҮ - е°ҶFPGAеҠҹиғҪйӣҶжҲҗеҲ°ASICдёӯпјҢеҸҜд»ҘжҸҗй«ҳзі»з»ҹзә§дҝЎеҸ·е®Ңж•ҙжҖ§пјҢ并ж¶ҲйҷӨдәҶеңЁPCBдёҠе®үиЈ…дёҖдёӘзӢ¬з«ӢFPGAзӣёе…іиҒ”зҡ„еҸҜйқ жҖ§е’ҢиүҜзҺҮжҚҹеӨұгҖӮ

д»ҘADASдёәдёӯеҝғзҡ„еӨ„зҗҶжЁЎеһӢ

з”ұдәҺеӨҡдёӘи§Ҷи§үеӨ„зҗҶзі»з»ҹзҡ„иһҚеҗҲиў«и®ӨдёәжҳҜй©ҫ驶иҫ…еҠ©е’ҢиҮӘеҠЁй©ҫ驶иҪҰиҫҶзҡ„ж ёеҝғпјҢжүҖд»Ҙе…Ҳиҝӣй©ҫ驶е‘ҳиҫ…еҠ©зі»з»ҹпјҲADASпјүеңЁжңӘжқҘзҡ„жұҪиҪҰжһ¶жһ„дёӯдҝқжҢҒдәҶж ёеҝғең°дҪҚпјҢеҚідҪҝиў«и®ӨдёәжҳҜз®ЎзҗҶиҖ…дёӯзҡ„з®ЎзҗҶиҖ…зҡ„еӨҡж ёи§Ҷи§үеӨ„зҗҶеҷЁпјҢд№ҹе·Із»ҸйғЁеҲҶиў«еҸ–д»ЈдәҶгҖӮж¶үеҸҠDSPе’Ңж•ҙж•°еҜҶйӣҶеһӢд»»еҠЎдёӨиҖ…зҡ„еӣҫеғҸе®һж—¶еӨ„зҗҶпјҢжңҖеҲқиў«и®ӨдёәжҳҜд»ҺйқҷжҖҒзӣёжңәжҲ–и§Ҷйў‘еӣҫеғҸдёӯжҸҗеҸ–дҝЎжҒҜд»ҘзЎ®е®ҡеҜ№иұЎзұ»еһӢгҖҒдҪҚзҪ®е’ҢйҖҹеәҰзҡ„й—®йўҳгҖӮйҡҸзқҖи®ҫи®Ўдәәе‘ҳдёәиҮӘеҠЁй©ҫ驶иҪҰиҫҶеҒҡеҮҶеӨҮпјҢADASеӨ„зҗҶеҷЁзҡ„и§’иүІе·Із»Ҹжү©еұ•еҲ°еҢ…жӢ¬и§Ҷи§үгҖҒзәўеӨ–гҖҒи¶…еЈ°жіўгҖҒжҝҖе…үйӣ·иҫҫпјҲLIDARпјүе’Ңйӣ·иҫҫеӣҫеғҸзҡ„иһҚеҗҲгҖӮеңЁдј з»ҹзҡ„SoCе’ҢеҚҸеӨ„зҗҶеҷЁеҘ—件дёӯпјҢеӣҫеғҸйў„еӨ„зҗҶдёҺCPUеҲҶејҖжү§иЎҢпјҢ并且еҝ…йЎ»йҖҡиҝҮдёҖдёӘжҲ–еӨҡдёӘй«ҳйҖҹжҖ»зәҝдёҺCPUиҝһжҺҘгҖӮеҚідҪҝADASжһ¶жһ„зҡ„жҖ»зәҝ延иҝҹеҫ—еҲ°ж”№е–„пјҢеҪ“еҚҸеӨ„зҗҶеҷЁеңЁеҚ•зӢ¬зҡ„иҠҜзүҮдёӯе®һзҺ°ж—¶пјҢд№ҹдјҡд»ҳеҮә延иҝҹзҡ„д»Јд»·гҖӮеӣ жӯӨпјҢе°ҶeFPGA IPдёҺз»ҹдёҖADASжһ¶жһ„дёӯзҡ„CPUзӣёз»“еҗҲпјҢд»ҘзЎ®дҝқеңЁеҝ«йҖҹеҸҳеҢ–зҡ„дәӨйҖҡзҠ¶еҶөдёӯжңүи§Ҷи§үгҖҒзәўеӨ–жҲ–йӣ·иҫҫиӯҰжҠҘзҡ„еҝ«йҖҹе“Қеә”пјҢиҝҷжҳҜеҸҜд»ҘйӘҢиҜҒзҡ„жңҖжңүж•Ҳзҡ„ж–№ејҸгҖӮ

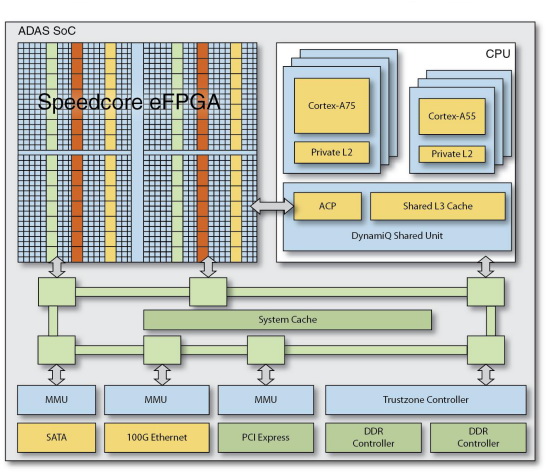

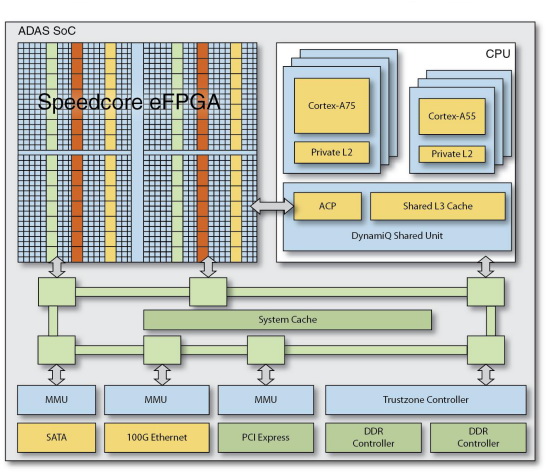

е°ҶеӨҡдёӘдј ж„ҹеҷЁжәҗдёҺдёҖдёӘADASеҶ…ж ёйӣҶжҲҗеңЁдёҖиө·пјҢжҸҗдҫӣдәҶSpeedcore IPдёҺдёҖдёӘCPU并иЎҢеөҢе…Ҙзҡ„дёҖз§ҚзҗҶжғіеә”з”ЁеңәжҷҜгҖӮ Speedcore IPж”ҜжҢҒе®ўжҲ·е°ҶдёҖдёӘе®ҡеҲ¶зҡ„еҸҜзј–зЁӢйҖ»иҫ‘йҳөеҲ—еөҢе…ҘеҲ°е…·жңүдё“з”Ёи®Ўз®—иө„жәҗзҡ„ж ҮеҮҶеҢ–ASICе№іеҸ°дёӯпјҲиҜ·еҸӮи§ҒдёӢеӣҫпјҢ并иҜ·еҸӮйҳ…第4йЎөпјүгҖӮеңЁе®һи·өдёӯпјҢиҝҷз§ҚйӣҶжҲҗеҢ–еҸҜд»Ҙе°Ҷд»ҺеӣҫеғҸжәҗжұҮжҖ»зҡ„ж•°жҚ®еҶҷе…ҘCPUзҡ„зј“еӯҳпјҢиҖҢдёҚжҳҜеҶҷе…ҘзӢ¬з«Ӣзҡ„SDRAMгҖӮ еҮҸе°‘CPUзҡ„дёӯж–ӯж„Ҹе‘ізқҖеҜ№з§»еҠЁдёӯжұҪиҪҰи§ҶйҮҺйҮҢзҡ„зү©дҪ“жңүжӣҙеӨҡзҡ„е®һж—¶е“Қеә”гҖӮ

и§Ҷи§үеӨ„зҗҶеҷЁпјҲйҖҡеёёжқҘиҮӘзӣёжңәиҫ“е…Ҙзҡ„2DеӣҫеғҸпјҢе°Ҫз®Ўе·ІеҢ…жӢ¬и¶ҠжқҘи¶ҠеӨҡзҡ„3DеӣҫеғҸпјүеҸҜд»Ҙдҫқйқ еӨҡе№ҙжқҘеңЁиҫ№зјҳжҸҗеҸ–гҖҒж јејҸиҪ¬жҚўгҖҒиүІеҪ©е№іиЎЎе’ҢеҲҶиҫЁзҺҮеҸҳеҢ–ж–№йқўз§ҜзҙҜзҡ„еӣҫеҪўеӨ„зҗҶеҷЁз ”究гҖӮеҢ…жӢ¬Cevaе’ҢSynopsysеңЁеҶ…зҡ„дёҖдәӣеӨ„зҗҶеҷЁIPдҫӣеә”е•ҶпјҢд№ҹеңЁеҜ№иұЎеҲҶзұ»е’ҢиҜҶеҲ«дёӯжҸҗеҚҮдәҶеҚ·з§ҜзҘһз»ҸзҪ‘з»ңзҡ„д»·еҖјгҖӮд»ҘNvidiaдёәд»ЈиЎЁзҡ„пјҢеңЁиҝҷдёӨдёӘйўҶеҹҹйғҪжңүз»ҸйӘҢзҡ„CPUдҫӣеә”е•ҶпјҢе·Із»ҸиҜ•еӣҫеңЁдј з»ҹзҡ„CPU / GPUд»»еҠЎдёҺзү№е®ҡзҡ„зҘһз»ҸзҪ‘з»ңжЁЎејҸиҜҶеҲ«еј•ж“Һд№Ӣй—ҙеҸ–еҫ—е№іиЎЎгҖӮеҜ№дәҺжұҪиҪҰдёӯзҡ„зҘһз»ҸзҪ‘з»ңеӯҗжһ¶жһ„пјҢжӯЈд»ҺйңҖиҰҒй«ҳзІҫеәҰжө®зӮ№DSPзҡ„ж—©жңҹжҲҗзҶҹжһ¶жһ„иҝҒ移еҲ°иғҪеӨҹдҪҝз”ЁдҪҺзІҫеәҰDSPеҶ…ж ёзҡ„иҮӘжҲ‘еҹ№и®ӯжҺЁзҗҶеј•ж“ҺпјҢSpeedcore DSP64жЁЎеқ—дёәж–°зҡ„ж·ұеәҰеӯҰд№ жһ¶жһ„жҸҗдҫӣдәҶеӨ§йҮҸзҡ„ејҖй”ҖгҖӮ еҜ№ADASе’Ңи§Ҷи§үеӨ„зҗҶжј”еҸҳзҡ„дёҖдёӘе…ұеҗҢи®ӨиҜҶжҳҜпјҢе®һж—¶жұҪиҪҰзҡ„жҖҒеҠҝж„ҹзҹҘж°ёиҝңдёҚдјҡжңүдёҖдёӘжңҖдҪізҡ„йӣҶдёӯејҸADASеӨ„зҗҶеҷЁжҲ–SoCгҖӮжҖ»жҳҜдјҡжңүж„ҸжғідёҚеҲ°зҡ„еҚҸеҗҢеӨ„зҗҶе’ҢеҠ йҖҹд»»еҠЎиў«ж·»еҠ еҲ°ADASдёӯеҝғеҶ…ж ёдёӯгҖӮ

д»»дҪ•ADASеӨ„зҗҶеҷЁеӣәжңүзҡ„дёӨйЎ№йҷ„еҠ еҠҹиғҪжҳҜдј ж„ҹеҷЁиһҚеҗҲ/дёӯжһўйӣҶжҲҗе’ҢзҪ‘з»ңиҪ¬жҚўгҖӮеүҚиҖ…ж¶үеҸҠе°ҶжқҘиҮӘеҗ„з§Қдј ж„ҹеҷЁзҡ„дҝЎжҒҜиҝӣиЎҢз»„еҗҲе’Ңе…іиҒ”пјҡеҢ…жӢ¬CMOSеӣҫеғҸгҖҒзәўеӨ–гҖҒжҝҖе…үйӣ·иҫҫе’Ңж–°е…ҙзҡ„е°ҸеһӢеҢ–йӣ·иҫҫзӯүдј ж„ҹеҷЁгҖӮзҪ‘з»ңиҪ¬жҚўжҳҜжҢҮд»ҘеӨӘзҪ‘зҡ„дё»е№ІзҪ‘з»ңдёҺCSI-2гҖҒFlexRayгҖҒCANз”ҡиҮіжӣҙж—©зҡ„зҪ‘з»ңеҚҸи®®зҡ„жҺҘеҸЈгҖӮиҷҪ然жңӘжқҘзҡ„дёҖдёӘADAS SoCзЎ®е®һеҸҜд»ҘйӣҶжҲҗдёҖдёӘдј ж„ҹеҷЁдёӯжһўжҲ–дёҖдёӘд»ҘеӨӘзҪ‘MACпјҢдҪҶжҖ»жҳҜдјҡжңүдёҖдәӣж–°е…ҙзҡ„еҠҹиғҪпјҢз”ұCPUеӨ–йғЁзҡ„еӨ–еӣҙйҖ»иҫ‘жһҒеҘҪең°жҸҗдҫӣгҖӮз”ұдәҺдј ж„ҹеҷЁиў«иҒҡеҗҲ并且зҪ‘з»ңеңЁиҫ“е…ҘеҲ°CPUд№ӢеүҚеңЁиҠҜзүҮеҶ…дә’иҝһпјҢжүҖд»ҘйҖҡиҝҮеҮҸе°‘жҡҙйңІзҡ„жҺҘеҸЈжқҘдҝқжҢҒе®үе…ЁжҖ§жҳҜдёҖдёӘи§ЈеҶіж–№жЎҲпјҢеҗҢж—¶йҖҡиҝҮзүҮдёҠйӣҶжҲҗжқҘжҸҗй«ҳеҸҜйқ жҖ§пјҢеҜ№дәҺи®ёеӨҡиҝҷж ·зҡ„д»»еҠЎиҖҢиЁҖе°Ҷиў«иҜҒжҳҺжҳҜжңҖдҪізҡ„ж–№жЎҲгҖӮ

еӣҫ1пјҡSpeedcoreйҳөеҲ—пјҲе·ҰдёҠпјүй“ҫжҺҘеҲ°CPUеӯҗзі»з»ҹеҸҠеҶ…еӯҳйӣҶзҫӨ

еҸҜзј–зЁӢиғҪеҠӣеңЁеҠҹиғҪе®үе…ЁжҖ§дёӯзҡ„дҪңз”Ё

д»Һй©ҫ驶иҫ…еҠ©иҪҰиҫҶеҲ°е®Ңе…ЁиҮӘеҠЁй©ҫ驶иҪҰиҫҶзҡ„иҝҮжёЎе·Із»ҸжҸҗй«ҳдәҶе®үе…ЁжҖ§еңЁж–°иҪҰдёӯзҡ„ең°дҪҚгҖӮзҪ‘з»ңеҜ№иҪҰиҫҶзҡ„жҺ§еҲ¶и¶ҠеӨҡпјҢи¶ҠеӨҡзҡ„еҸёжңәжңҹжңӣеӨҡзә§е®үе…ЁжҖ§д»ҘйҳІжӯўиҜёеҰӮеј•иө·дәҶе…¬дј—й«ҳеәҰе…іжіЁзҡ„2016е№ҙзү№ж–ҜжӢүжӯ»дәЎдәӢж•…иҝҷзұ»дәӢ件гҖӮиҝҷз§ҚеҜ№дәҺе®№й”ҷе®үе…ЁжҖ§зҡ„й©ұеҠЁеҠӣдҝғдҪҝдёҡз•ҢйўҒеёғдәҶй’ҲеҜ№иҮӘеҠЁй©ҫ驶жұҪиҪҰйўҶеҹҹзҡ„ISO 26262ж ҮеҮҶпјҢе®ғжҳҜдҪңдёәз”өж°”е’Ңз”өеӯҗзі»з»ҹIEC 61508йҖҡз”ЁеҠҹиғҪе®үе…ЁжҖ§ж ҮеҮҶзҡ„иЎҚз”ҹж ҮеҮҶгҖӮ

еңЁEDAе’ҢSoCзӨҫзҫӨеҶ…зҡ„ж—©жңҹе·ҘдҪңе·Із»Ҹе®һзҺ°дәҶISO 26262ж–№жі•дҪ“зі»зҡ„ж ҮеҮҶеҢ–пјҢд»ҘзЎ®дҝқIPдёӯеҠҹиғҪе®үе…ЁжҖ§гҖӮж•…йҡңжЁЎејҸгҖҒж•Ҳжһңе’ҢиҜҠж–ӯеҲҶжһҗпјҲFMEDAпјүжҠҖжңҜйҳҗиҝ°дәҶй’ҲеҜ№IPеҚ•е…ғзҡ„еҠҹиғҪе’Ңж•…йҡңжЁЎејҸзҡ„ж ҮеҮҶ规иҢғпјҢдёҖдёӘж•…йҡңжЁЎејҸеҜ№дә§е“ҒеҠҹиғҪзҡ„еҪұе“ҚпјҢиҮӘеҠЁиҜҠж–ӯжЈҖжөӢж•…йҡңзҡ„иғҪеҠӣпјҢи®ҫи®ЎејәеәҰд»ҘеҸҠиҝҗиЎҢжғ…еҶөеҲҶйӣҶпјҢеҢ…жӢ¬зҺҜеўғеҺӢеҠӣгҖӮдёҖдёӘејәеҒҘзҡ„зі»з»ҹеә”иҜҘжңҖеӨ§йҷҗеәҰең°жҸҗй«ҳIPеҚ•е…ғзҡ„иҜҠж–ӯиҰҶзӣ–иҢғеӣҙпјҢ并йҖҡиҝҮйҖӮеҪ“еӨ„зҗҶе®үе…Ёзҡ„гҖҒжЈҖжөӢеҲ°зҡ„е’ҢжңӘжЈҖжөӢеҲ°зҡ„ж•…йҡңжқҘжҸҗдҫӣй«ҳеәҰзҡ„еҠҹиғҪе®үе…ЁжҖ§гҖӮ

еөҢе…ҘејҸFPGAз”ұдәҺе…¶жһҒеәҰеҸҜзј–зЁӢеҢ–зҡ„зү№жҖ§пјҢиҝҳеҸҜд»ҘеўһејәиҪҰиҫҶеңЁдҪңдёәзі»з»ҹж—¶зҡ„е®үе…ЁжҖ§гҖӮ йҷӨдәҶдё»жҺ§иҪҰиҫҶзҡ„вҖңиҲӘиЎҢвҖқеҠҹиғҪд№ӢеӨ–пјҢSoCдёӯзҡ„eFPGAиҝҳеҸҜд»ҘжүҝиҪҪеӨ§йҮҸзҡ„硬件иҜҠж–ӯеҠҹиғҪпјҢе…¶иҝҗиЎҢйҖҹеәҰжҜ”еҹәдәҺиҪҜ件зҡ„иҜҠж–ӯеҝ«еҮ дёӘж•°йҮҸзә§пјҢеӨ§еӨ§еўһеҠ дәҶд»»дҪ•иҪҰиҪҪеҶ…зҪ®зҡ„иҮӘжөӢж•…йҡңиҰҶзӣ–зҺҮпјҲBISTпјүгҖӮ жӯӨеӨ–пјҢе®ғ们д»ҘеҸҜзј–зЁӢж–№ејҸеё®еҠ©жұҪиҪҰеҲ¶йҖ е•Ҷжӣҙж–°е·ІйғЁзҪІзҡ„зі»з»ҹпјҢд»ҺиҖҢжңүеҠ©дәҺISO 26262е®үе…ЁжҖ§з”ҹе‘Ҫе‘ЁжңҹгҖӮ д»Ҙзү№ж–ҜжӢүиҪҰзҘёдёәдҫӢпјҢеҰӮжһңдәӢж•…зҡ„ж №жң¬еҺҹеӣ жҳҜ硬件дёӯжүҳз®Ўзҡ„еҜ№иұЎжЈҖжөӢз®—жі•дёӯжңүй”ҷиҜҜпјҲз”ұдәҺжҖ§иғҪеҺҹеӣ пјүпјҢеҸӘиҰҒејҖеҸ‘дәҶдҝ®еӨҚзЁӢеәҸпјҢе°ұеҸҜд»Ҙе°Ҷе…¶жҺЁйҖҒеҲ°ж•ҙдёӘиҪҰйҳҹгҖӮеҸҜд»Ҙз»•иҝҮжј«й•ҝиҖҢжҳӮиҙөзҡ„硬件ејҖеҸ‘е’ҢйҮҚж–°йғЁзҪІиҝҮзЁӢгҖӮ

еҲҶеёғејҸжҺ§еҲ¶ж„Ҹе‘ізқҖеҲҶеёғејҸжҷәиғҪ

з”ұдәҺж‘„еғҸеӨҙзҡ„е®үиЈ…дҪҚзҪ®д»ҘеҸҠеҜ№еұҖйғЁдј ж„ҹеҷЁдёӯжһўзҡ„йңҖжұӮпјҢжұҪиҪҰи®ҫи®Ўдәәе‘ҳжҖ»жҳҜ规еҲ’еңЁиҪҰдҪ“еҶ…йҮҮз”ЁдәҶеӨ§йҮҸзҡ„еҲҶеёғејҸжҷәиғҪгҖӮе°Ҫз®ЎеҰӮжӯӨпјҢиҜёеҰӮNvidia TegraзӯүеӨҡж ёеӨҡзәҝзЁӢеӨ„зҗҶеҷЁзҡ„ж—©жңҹж”ҜжҢҒиҖ…йғҪи®ӨдёәпјҢиҰҒжҠҠеӨ§йғЁеҲҶжҷәиғҪйғҪйӣҶдёӯеңЁд»ӘиЎЁжқҝдёӯжҲ–иҖ…йҷ„иҝ‘пјҢе°Ҫз®ЎжҳҜдёәдәҶй«ҳеәҰ并иЎҢзҡ„CPUе·ҘдҪңдәҺеҜ№иұЎиҜҶеҲ«гҖӮзҺ°еңЁпјҢе…Ҳиҝӣзҡ„ADASеңЁиҫ…еҠ©й©ҫ驶жұҪиҪҰе’Ңдёүзә§иҮӘдё»й©ҫ驶жұҪиҪҰзҡ„е®Ңе…ЁиҮӘдё»жҖ§д№Ӣй—ҙзҡ„жЁЎзіҠз•Ңйҷҗе·Із»Ҹеј•иө·дәә们зҡ„жіЁж„ҸпјҢеӣһеҲ°еҲҶеёғејҸжҷәиғҪпјҢе…¶дёӯCPUгҖҒGPUе’ҢзҘһз»ҸзҪ‘з»ңеӨ„зҗҶеҷЁеңЁиҪҰдҪ“еҶ…жҸҗдҫӣдәҶеӨҡдёӘз®ЎзҗҶе’ҢжҺ§еҲ¶зӮ№гҖӮиҝҷз§ҚиҪ¬еҸҳж„Ҹе‘ізқҖеҸҜзј–зЁӢжһ¶жһ„зҡ„жӣҙеӨҡжңәдјҡеӯҳеңЁдәҺе…ЁйқўиҰҶзӣ–зҡ„SoCи®ҫи®Ўд№ӢеӨ–гҖӮ

зҺ°еңЁпјҢADASеӨ„зҗҶеҷЁеёӮеңәжҜҸе№ҙеўһй•ҝи¶…иҝҮ25пј…гҖӮиҝҷз§Қеўһй•ҝжҳҜз”ұдәҺд»ҺиҮӘеҠЁзҙ§жҖҘеҲ¶еҠЁгҖҒжҚўйҒ“иҫ…еҠ©е’ҢиҮӘйҖӮеә”е·ЎиҲӘжҺ§еҲ¶зӯүеҠҹиғҪејҖе§ӢпјҢADASеҠҹиғҪе·Ід»ҺиұӘеҚҺиҪҰиҫҶиҪ¬з§»еҲ°дёӯеһӢе’Ңе…Ҙй—Ёзә§иҪҰиҫҶ - иҝҷдәӣеҠҹиғҪе°ҶеңЁдёӢдёӘеҚҒе№ҙдёӯжңҹд№ӢеүҚиў«жҷ®йҒҚдҪҝз”ЁгҖӮдёҺжӯӨеҗҢж—¶пјҢдёүзә§иҮӘеҠЁй©ҫ驶жұҪиҪҰе°ҶдәҺ2018е№ҙеңЁиҜёеҰӮе®қ马17зӯүиұӘеҚҺе№іеҸ°дёҠжҺЁеҮәпјҢиҖҢе…ЁиҮӘеҠЁдә”зә§жұҪиҪҰеҸҜиғҪеңЁ2022е№ҙд№ӢеүҚеҸҜдҫӣе•Ҷдёҡй”Җе”®гҖӮйҡҸзқҖиҮӘдё»й©ҫ驶平еҸ°д»Һдёүзә§еҸ‘еұ•еҲ°еӣӣзә§е’Ңдә”зә§пјҢдј ж„ҹеҷЁдёӯжһўгҖҒж‘„еғҸеӨҙе’ҢжҝҖе…үйӣ·иҫҫ/йӣ·иҫҫи®ҫеӨҮе°ҶйҒҚеёғж•ҙдёӘиҪҰиҫҶпјҢ并且жҜҸдёӘйғҪйңҖиҰҒжң¬ең°жҺ§еҲ¶гҖӮ

иҝҷз§ҚжҺ§еҲ¶жЁЎејҸеңЁдёҡз•Ңдә§дёҡж•ҙеҗҲдёӯе·Із»Ҹжё…жҷ°еҸҜи§ҒпјҢеҰӮй«ҳйҖҡе…¬еҸёеҜ№жҒ©жҷәжөҰеҸ‘иө·зҡ„收иҙӯгҖҒд»ҘеҸҠиӢұзү№е°”еҜ№Mobileyeзҡ„收иҙӯпјҢеӨ„зҗҶеҷЁйўҶеҹҹе°Ҷз”ұйӮЈдәӣиҮҙеҠӣдәҺе°ҶејҖеҸ‘з”ҹжҖҒзі»з»ҹеј•еҜјиҮізү№е®ҡдё“дёҡйўҶеҹҹзҡ„еӨ§еһӢдҫӣеә”е•ҶеҚ жҚ®дё»еҜјең°дҪҚ вҖ” иӢұзү№е°”йҮҮз”ЁжңҚеҠЎеҷЁеҠ жңәеҷЁеӯҰд№ жЁЎејҸпјҢиӢұдјҹиҫҫйҮҮз”ЁGPU /жңәеҷЁеӯҰд№ жЁЎејҸпјҢй«ҳйҖҡйҮҮз”Ёд»ҘиңӮзӘқ移еҠЁйҖҡдҝЎдёәдёӯеҝғзҡ„жЁЎејҸпјҢеўһеҠ дәҶжҒ©жҷәжөҰCognivueе’Ңi.MXеӨ„зҗҶеҷЁгҖӮдҫӢеҰӮ CevaгҖҒCadence / TensilicaгҖҒSynopsys / ARCе’ҢVeriSiliconзӯүIPејҖеҸ‘дәәе‘ҳе°Ҷе°қиҜ•йҖҡиҝҮе…¶еңЁзү№ж®ҠеӨ„зҗҶеҷЁеҶ…ж ёж–№йқўзҡ„дё“дёҡжҠҖжңҜжқҘйў иҰҶе°Ғй—ӯжЁЎејҸгҖӮдёҺжӯӨеҗҢж—¶пјҢеҰӮBroadcomгҖҒValensе’ҢMarvellзӯүзҪ‘з»ң专家е°ҶеҜ»жұӮеӣҙз»•д»ҘеӨӘзҪ‘дё»е№ІзҪ‘з»ңжқҘе®ҡд№үжұҪиҪҰжһ¶жһ„гҖӮ

иҝҷж ·зҡ„еёӮеңәж јеұҖдёҺдјҒдёҡзҪ‘з»ңжј”еҸҳжҲҗж•°жҚ®дёӯеҝғзҡ„ж—¶д»ЈжңүдәӣзӣёдјјгҖӮд»ҘеӨ„зҗҶеҷЁдёәдёӯеҝғзҡ„еҚҠеҜјдҪ“дҫӣеә”е•ҶиҜ•еӣҫе®ҡд№үдёҖдёӘе®Ңж•ҙзҡ„зі»з»ҹжһ¶жһ„пјҢдҪҶи®ҫи®ЎйўҶеҹҹеҲҷеұ•зӨәдәҶеӨҡж ·еҢ–зҡ„зӢӮйҮҺиҘҝйғЁпјҲWild-WestпјүйЈҺж јпјҢе…¶дёӯз”ЁдёҚеҗҢзҡ„йҖ»иҫ‘еҘ—件жқҘдёәдёҖ家组件дҫӣеә”е•ҶпјҲд»ҘеҸҠOEMжҲ–жұҪиҪҰеҲ¶йҖ е•ҶпјүжҸҗдҫӣж ·е“Ғд»ҺиҖҢеҲӣе»әзү№жңүзҡ„дјҳеҠҝгҖӮеңЁиҝҷж ·зҡ„зҺҜеўғдёӯпјҢй…ҚзҪ®дёәIPзҡ„еҸҜзј–зЁӢйҖ»иҫ‘пјҲеҰӮAchronixзҡ„Speedcore eFPGAпјүе°Ҷжү®жј”йҮҚиҰҒи§’иүІпјҢдёҚд»…еңЁиҝ‘жңҹиҫ…еҠ©й©ҫ驶е’ҢиҮӘеҠЁй©ҫ驶жұҪиҪҰејҖеҸ‘ж–№йқўжҳҜиҝҷж ·пјҢиҖҢдё”еңЁиҝҷдёӨз§Қзұ»еһӢзҡ„иҪҰиҫҶеӨҡе№ҙжқҘзҡ„еҲҶеёғејҸеӨ„зҗҶеҷЁејҖеҸ‘еҸ‘йқўдәҰжҳҜеҰӮжӯӨгҖӮ

Speedcore eFPGA IPжҸҗдҫӣдәҶе…¶д»–дјҳеҠҝпјҢдҫӢеҰӮйҖҡиҝҮеҶҷе…ҘCPUзј“еӯҳиҖҢдёҚжҳҜзүҮеӨ–еҶ…еӯҳжқҘжңҖеӨ§йҷҗеәҰең°еҮҸе°‘CPUдёӯж–ӯгҖӮ CANи®ҫи®ЎдёӯжүҖйңҖзҡ„BISTз”өи·ҜйҖҡеёёеҚ жҖ»ASICз”өи·Ҝзҡ„10пј…иҮі15пј…пјҢз”ұдәҺж”ҜжҢҒBISTзҡ„з”өи·ҜеҸҜд»ҘеңЁeFPGAеҶ…еҸҜзј–зЁӢпјҢжүҖд»ҘеңЁи®ёеӨҡжғ…еҶөдёӢиҝҷдәӣз”өи·ҜеҸҜд»Ҙиў«зңҒеҺ»гҖӮ еҸҰеӨ–пјҢeFPGAеҸҜд»ҘжҸҗдҫӣзүҮдёҠжҺўжөӢеҠҹиғҪжқҘиҝӣиЎҢиҜҠж–ӯгҖӮеҜ№дәҺзҺ°жңүзҡ„еҹәдәҺASICзҡ„гҖҒж— йңҖжӣҙжҚўFPGAзҡ„зі»з»ҹи®ҫи®ЎпјҢSpeedcore IPжүҖе…·жңүзҡ„зҒөжҙ»жҖ§е°Ҷж”ҜжҢҒеҜ№ж–°з®—жі•иҝӣиЎҢзј–зЁӢпјҢд»ҺиҖҢ延й•ҝдәҶзҺ°еңәе·ІйғЁзҪІзҡ„ASICзҡ„дҪҝз”ЁеҜҝе‘ҪгҖӮеңЁ5GиңӮзӘқзҪ‘з»ңзҺ°жңүи®ҫи®ЎдёӯдҪҝз”ЁSpeedcore IPд№ҹе°ҶдҪҝиҜҘжһ¶жһ„жҲҗдёәжңӘжқҘV2XйҖҡдҝЎжҺҘеҸЈзҡ„зҗҶжғіеһӢйҖүжӢ©гҖӮ

еңЁжңӘжқҘзҡ„е…ЁиҮӘеҠЁе’Ңе…Ҳиҝӣиҫ…еҠ©й©ҫ驶иҪҰиҫҶдёӯпјҢеӯҳеңЁеҮ еҚҒдёӘз”ҡиҮіж•°зҷҫдёӘеҲҶеёғејҸCPUгҖӮ з”ЁдәҺе°ҶжұҪиҪҰеӯҗзҪ‘иҝһжҺҘеңЁдёҖиө·зҡ„еӨ–и®ҫеӨ„зҗҶеҠҹиғҪеҸҜз”ұASICгҖҒSoCжҲ–дј з»ҹFPGAжҸҗдҫӣжңҚеҠЎгҖӮ дҪҶжҳҜпјҢSpeedcore eFPGA IPзҡ„еј•е…ҘжҸҗдҫӣдәҶдј з»ҹFPGAжүҖдёҚе…·еӨҮзҡ„пјҢеңЁе»¶иҝҹгҖҒе®үе…ЁжҖ§гҖҒеёҰе®Ҫе’ҢеҸҜйқ жҖ§зӯүж–№йқўзҡ„дјҳеҠҝгҖӮ(end)

|

|

| ж–Үз« еҶ…е®№д»…дҫӣеҸӮиҖғ

(жҠ•зЁҝ)

(10/30/2018) |

еҜ№ жұҪиҪҰз”өеӯҗ жңүдҪ•и§Ғи§ЈпјҹиҜ·еҲ° жұҪиҪҰз”өеӯҗи®әеқӣ з•…жүҖж¬ІиЁҖеҗ§пјҒ

|