|

二极管、三极管 |

|

| 按行业筛选 |

|

|

| 按产品筛选 |

|

|

| |

|

查看本类全部文章 |

| |

|

|

|

|

提高4H-SiC肖特基二极管和MOSFET的雪崩耐受性 |

|

|

作者:Amaury Gendron-Hansen |

|

半导体市场的最新趋势是广泛采用碳化硅(SiC)器件,包括用于工业和汽车应用的肖特基势垒二极管(SBD)和功率MOSFET。与此同时,由于可供分析的现场数据有限,这些器件的长期可靠性成为一个需要解决的热点问题。一些SiC供应商已开始根据严格的工业和汽车(AEC-Q101)标准来认证SiC器件,而另一些供应商不但超出了这些认证标准的要求,还能为恶劣环境耐受性测试提供数据。为了使SiC器件在任务和安全关键型应用中保持较高的普及率,应将这种认证和测试策略与特定的设计规则相结合来实现高雪崩耐受性,这一点至关重要。

市场快速增长

SiC器件的市场份额预计将在未来几年加速增长,主要推动因素是运输行业的电气化。SiC管芯将成为车载充电器和动力传动牵引系统等应用的模块中的基本构件。由于雪崩击穿的临界电场较高,因此高压SiC器件的外形比同类硅器件小得多,并且可以在更高的开关频率下工作。SiC的热性能也十分出色,它不但拥有良好的散热性能,还能在高温下工作。实际上,最高工作温度通常可达175 °C,很少超过200 °C,主要限制为装配工艺(焊接金属和封装材料)。SiC器件本质上比硅器件更高效,切换到SiC管芯可以极大减少模块中单个管芯的数量。

随着SiC器件从利基市场转向主流市场,与大规模生产爬坡效应相关的主要挑战正逐渐被克服。为轻松实现这种转变,制造厂正在建立可与现存硅生产线共用工具的SiC生产线。这种安排可有效降低SiC管芯的成本,因为这样做可与Si生产线分担开销。随着晶圆供应商大幅度提高产能,近来在晶圆供货方面的限制已不再是问题。由于4H-SiC衬底和外延生长的不断改进,现在可提供晶体缺陷密度极低的高质量6英寸晶圆。根据电气参数测试可知,晶圆质量越高,SiC器件的产量就越高。

但请务必记住,由于这些器件仅仅上市几年,因此其现场可靠性数据十分有限。此外,由于SiC器件自身也面临着一系列挑战,因此其认证比硅器件的认证困难得多。在SiC器件中,反向偏置条件下的电场高出将近一个数量级。如果不采用适当的设计规则,这种高电场很容易损坏栅极氧化层。SiC栅极氧化层界面附近的陷阱密度也高得多。结果是,由于陷阱带电,因此老化测试期间可能会出现不稳定性。一直以来,我们都专注于提高长期可靠性,而取得的成果也令人欣慰,最近的报告显示器件已通过严格的工业和汽车(AEC-Q101)标准认证。

除此之外,SiC供应商也已开始采取下一步行动,即为恶劣环境耐受性测试提供数据。

恶劣环境耐受性测试

作为示例,Microchip通过子公司Microsemi在其适用于700V、1200V和1700V电压节点的SiC SBD和MOSFET上进行了恶劣环境耐受性测试。测试表明,高水平的非钳位感应开关(UIS)耐受性对于保证器件的长期可靠性至关重要。同时还表明,在UIS测试期间,高瞬态电流流过反向偏置器件,并驱动其进入雪崩击穿状态。在高电流和高电压的共同作用下,会产生大量热量且温度急剧上升。耐用功率MOSFET的局部最高温度可达到500°C,远高于典型温度额定值。

UIS的耐受性与生产线前端和后端的外延质量和制造工艺密切相关。即使外延中的微小晶体缺陷或与工艺相关的缺陷也可能构成薄弱环节,导致器件在UIS测试期间过早失效。这就解释了为什么对产品系列耐受性的全面分析中应当包含单脉冲和重复UIS(RUIS)测试。

单脉冲测试用作筛选测试,用于识别UIS耐受性较低的器件。为了保证产品数据手册中的UIS额定值,所有器件在交付给客户之前都应经过测试。不过,器件在现场投入使用期间可能会经历多次UIS事件。为了分析逐渐磨损的特性,需要重复测试。要深入分析特性,应对器件施加大量脉冲,常见做法是100,000次冲击。

在UIS脉冲期间,被测器件中的电流连续降低,而电压基本保持恒定,但会因热效应而略微变化(图1)。UIS脉冲的能量由脉冲开始时的最大电流和负载的电感定义。在测试过程中,通过改变电感值来调节能量。最大电流保持恒定;它等于SBD的正向电流额定值,也等于MOSFET的漏极电流额定值的三分之二。

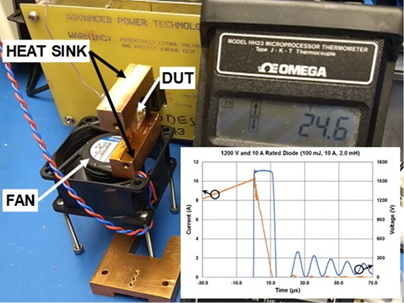

图1:UIS脉冲期间的RUIS测试设置以及电流和电压的波形

RUIS测试具有特定的约束条件,主要目的是防止一个脉冲与下一个脉冲的温度发生积聚。在施加新脉冲之前,务必确保器件温度接近环境温度。在图1所示的测试设置中,使用热电偶传感器监视器件的温度,并调整脉冲重复频率以获得恒定的读数。为了有助于冷却器件,应将其安装在散热器上风扇下方的位置。

可实现高雪崩耐受性的器件设计

除了采用适当的测试过程之外,一流的UIS耐受性还需要使用下面的一组设计规则:

高压端接设计有足够高的固有击穿电压,以确保有效区域首先进入雪崩状态。在这种情况下,能量会分散到整个有效区域上,而不是在狭窄的端接中,后一种情况会导致过早失效。

MOSFET的JFET区域中的电场屏蔽对于保护栅极氧化层非常关键。应当谨慎优化用于界定JFET区域的P型掺杂阱的设计和注入方案,以便提供足够的屏蔽而不会严重影响导通状态电阻。

利用具有高导热率的钝化材料为热量通过管芯的顶部耗散提供了路径。

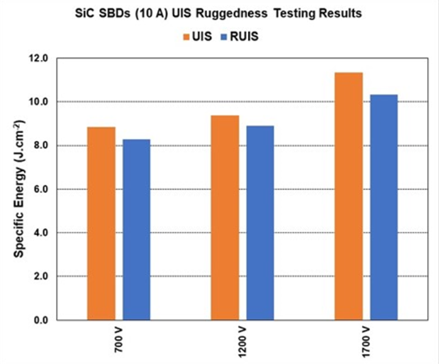

使用这些规则设计的肖特基二极管和功率MOSFET在恶劣环境耐受性测试中均表现良好。对SBD的测试持续到单脉冲和重复UIS失效为止,同时还监视了多个直流参数。这项测试的结果表明,器件的正向电压和反向泄漏电流十分稳定,而反向击穿电压则略有增加,这可归因于SiC上表面附近的自由载流子俘获。即将失效之前的脉冲能量如图2所示。UIS耐受性随器件额定电压的增大而提高。鉴于大部分热量在外延区域产生,这种趋势不难解释。随着外延厚度因额定电压的增大而增加,每单位体积产生的热量会减少,这反过来会降低器件中的温度。由于重复测试的原因,UIS的耐受性会系统性降低,但程度很小。与单脉冲UIS相比,差异小于10%。多个UIS脉冲没有强累加效应,预计SBD在现场投入使用期间将保持高耐受性。

图2:700V、1200V和1700V SiC SBD失效前每个活动区域的比能

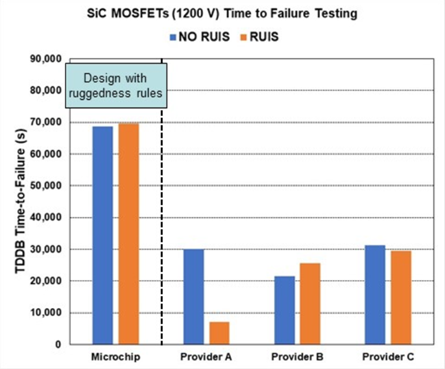

MOSFET恶劣环境耐受性特性分析应重点关注栅极氧化层的长期可靠性,这无需对器件施压至失效。作为替代,可使用由100,000个能量相对较低的脉冲组成的重复测试。举例来说,Microsemi 1200V/40 mΩ MOSFET使用雪崩耐受性规则进行设计,通过100 mJ脉冲进行测试,其单脉冲UIS额定值为2.0J。大多数直流参数不受影响;不过,由于该测试对栅极氧化层施压,因此会观察到栅极泄漏的适度增加。为了确定长期可靠性是否受到损害,我们对器件施加了随时间变化的介电击穿。图3报告了对各种器件的栅极施加50 µA直流电流时的失效时间,具体包括使用公司的雪崩耐受性规则开发的Microsemi SiC器件以及其他三家领先供应商提供的器件。

图3:四家供应商提供的1200V MOSFET的TDDB失效时间

坚持采用SiC

在工业和汽车市场中采用SiC器件时,需满足严格的长期可靠性要求。满足这些要求的最佳策略是使产品通过汽车AEC-Q101标准认证,并对尚未标准化的极端环境耐受性测试进行特性分析。通过应用设计规则来实现高雪崩耐受性同样十分重要。这些措施一起使用时,不仅有助于确保SiC器件在快速普及的道路上继续前进,同时还能提供这些应用所需的长期可靠性。(end)

|

|

| 文章内容仅供参考

(投稿)

(8/15/2020) |

对 二极管、三极管 有何见解?请到 二极管、三极管论坛 畅所欲言吧!

|